Data Sheet, V0.4, Apr. 2008

# TC1792 32-Bit Single-Chip Microcontroller TriCore

Microcontrollers

Never stop thinking

Edition 2008-04 Published by Infineon Technologies AG 81726 Munich, Germany © 2008 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## TC1792 32-Bit Single-Chip Microcontroller TriCore

## Microcontrollers

Never stop thinking

| TC1792 Da<br>Advance I<br>Revision F | nformation                                                            | 2008-04                           | V0.4 |  |  |  |  |  |  |

|--------------------------------------|-----------------------------------------------------------------------|-----------------------------------|------|--|--|--|--|--|--|

| Previous V                           | ersion:                                                               | V0.3                              |      |  |  |  |  |  |  |

| Page                                 | Subjects (m                                                           | ajor changes since last revision) |      |  |  |  |  |  |  |

| 1-7                                  | Design step                                                           | AB: added in synopsis.            |      |  |  |  |  |  |  |

| 2-9, 2-10                            | Figure corre                                                          | Figure corrected.                 |      |  |  |  |  |  |  |

| 2-12                                 | NC pin list c                                                         | NC pin list corrected.            |      |  |  |  |  |  |  |

| 2-30                                 | VSS pin list corrected.                                               |                                   |      |  |  |  |  |  |  |

| 3-71                                 | Figure corrected.                                                     |                                   |      |  |  |  |  |  |  |

| 3-74                                 | Design step AB: RTID value provided.                                  |                                   |      |  |  |  |  |  |  |

| 4-80                                 | The description of the inactive device current improved               |                                   |      |  |  |  |  |  |  |

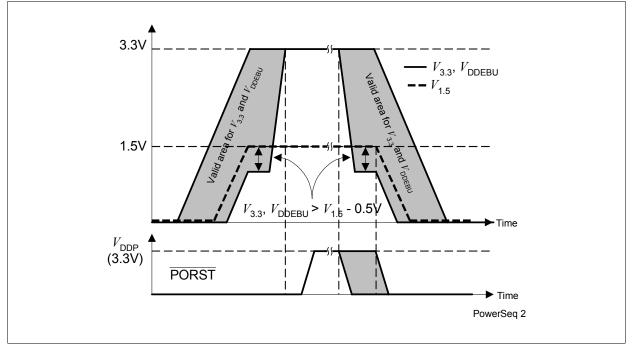

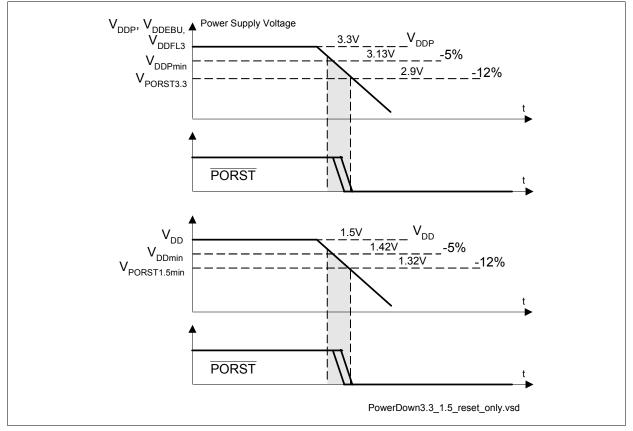

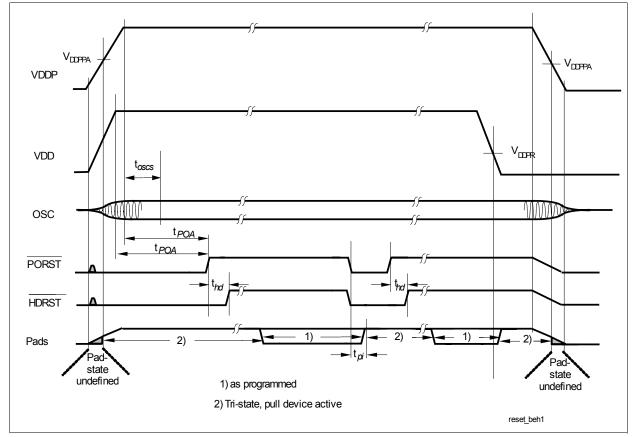

| 4-99                                 | The description of the power-up sequence improved                     |                                   |      |  |  |  |  |  |  |

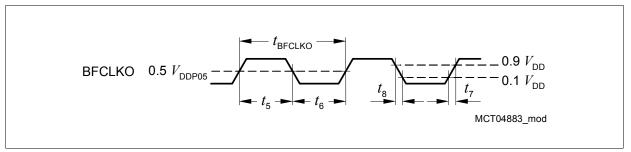

| 4-106                                | BFCLKO clock, duty cycle description extended.                        |                                   |      |  |  |  |  |  |  |

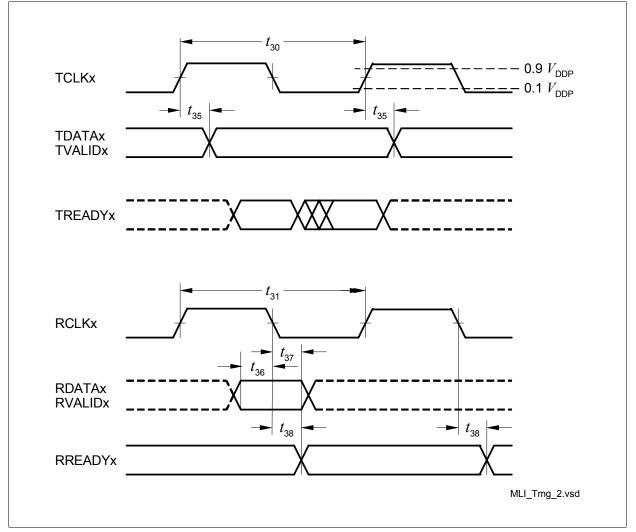

| 4-117                                | MLI timing, maximum operating frequency limit extended, t31 added.    |                                   |      |  |  |  |  |  |  |

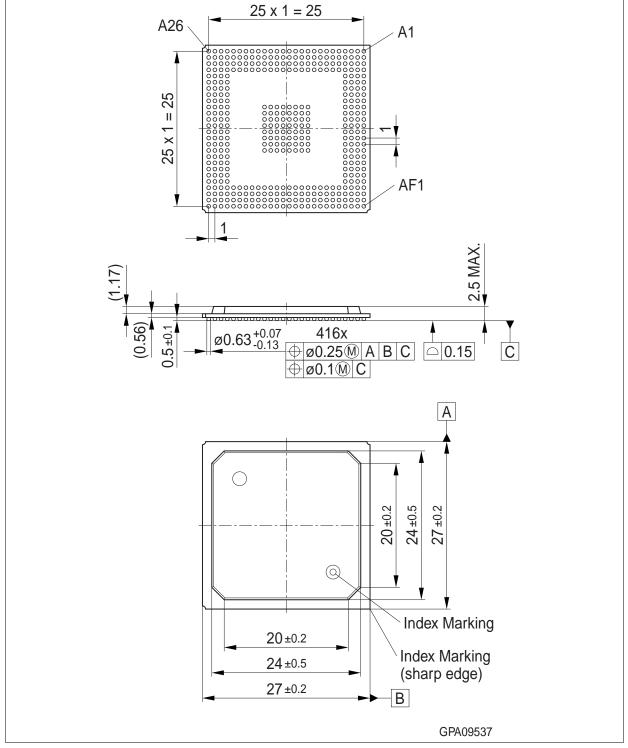

| 5-121                                | Design step AB: additional package added                              |                                   |      |  |  |  |  |  |  |

| 5-123                                | Data Flash size and consequently the EEPROM emulation data corrected. |                                   |      |  |  |  |  |  |  |

| 5-124                                | Example of                                                            | temperature profile corrected.    |      |  |  |  |  |  |  |

TriCore® is a trademark of Infineon Technologies AG.

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

## Table of Contents

TC1792

## **Table of Contents**

| 1                                                                                                                                                                                                                 | Summary of Features                                                                                                                                                                                                                | 5                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                                                                                                                                                                | General Device Information         Block Diagram         Logic Symbol         Pin Configuration         Pad Driver and Input Classes Overview         Pin Definitions and Functions         Pull-Up/Pull-Down Behavior of the Pins | 8<br>9<br>10<br>11<br>12                                                               |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.14.1<br>3.15<br>3.16<br>3.17<br>3.18<br>3.19<br>3.20<br>3.21<br>3.22<br>3.23<br>3.24<br>3.25 | Power Management System         On-Chip Debug Support         Clock Generation and PLL         Power Supply                                                                                                                        | 31<br>32<br>34<br>35<br>37<br>39<br>41<br>45<br>47<br>49<br>51<br>55<br>57<br>61<br>63 |

| <b>4</b><br>4.1<br>4.1.1<br>4.1.2                                                                                                                                                                                 |                                                                                                                                                                                                                                    |                                                                                        |

#### **Table of Contents**

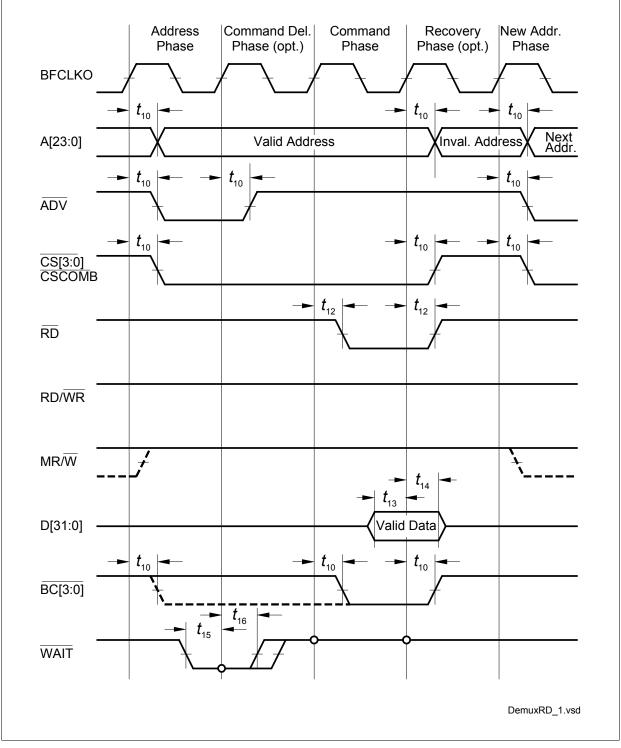

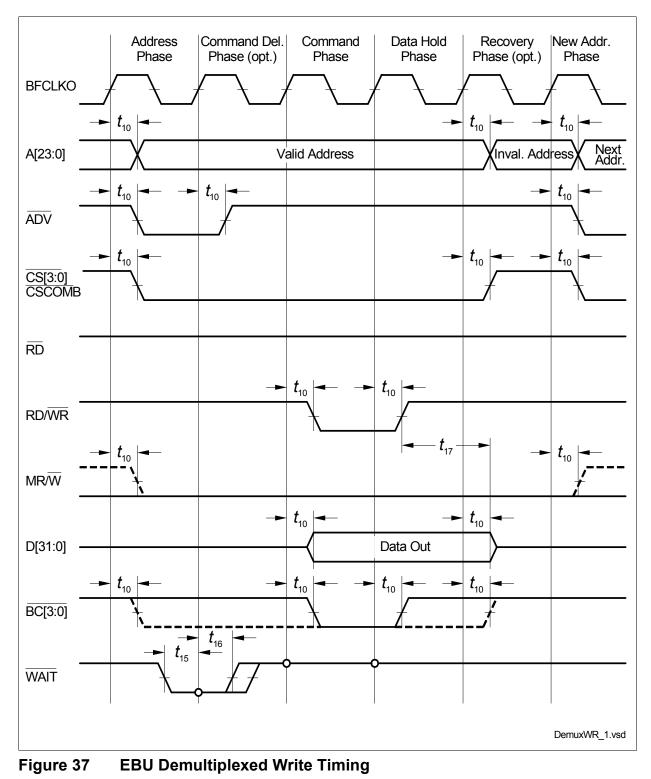

| Demultiplexed Read Timing  | 79<br>82<br>85<br>91<br>95<br>95<br>96<br>97<br>98<br>97<br>98<br>97<br>101<br>103<br>106<br>108<br>109<br>111<br>112<br>113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

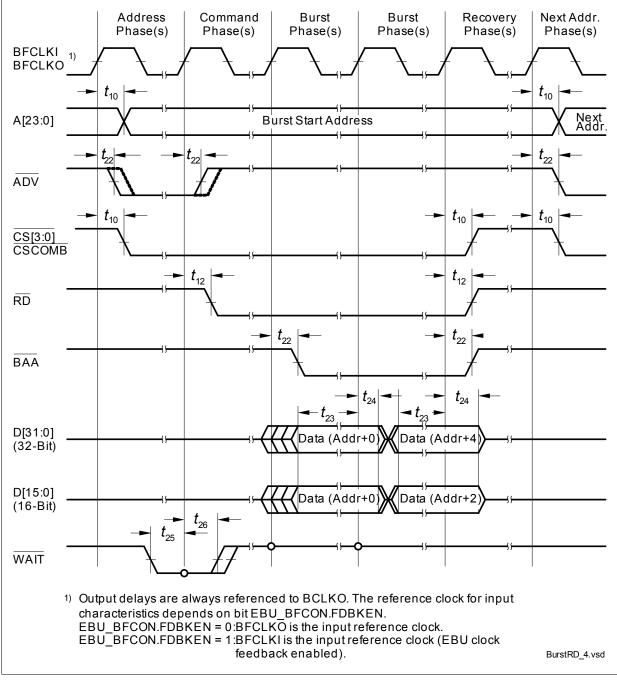

| EBU Burst Mode Read Timing |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                            | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                            | 119<br>120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                            | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                            | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Package Outline            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Flash Memory Parameters    | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Quality Declarations       | 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

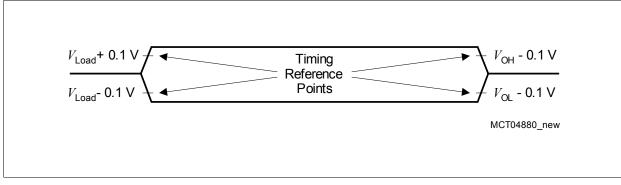

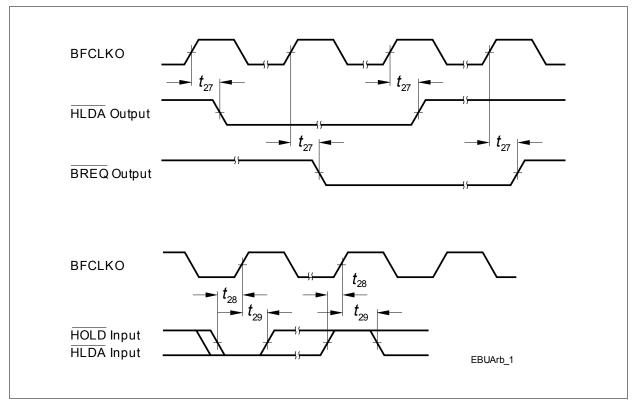

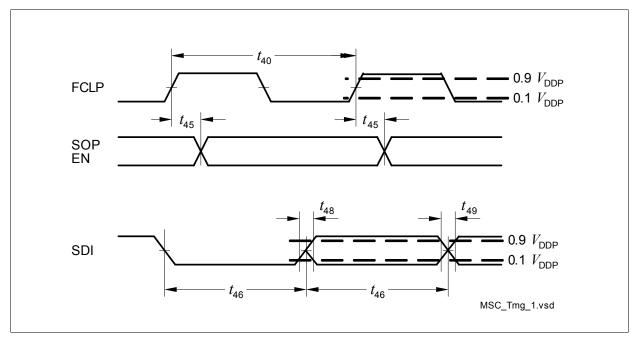

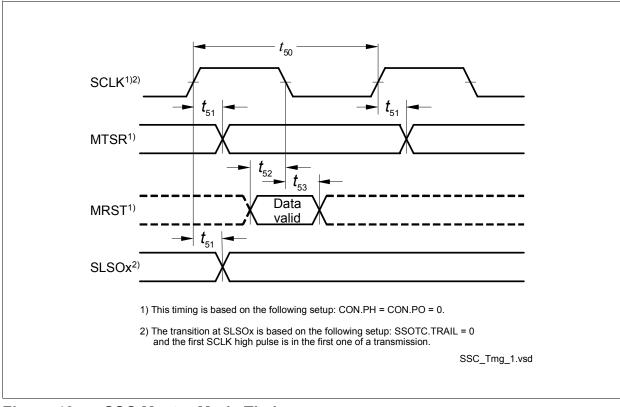

|                            | Operating Conditions         DC Parameters         Input/Output Pins         Analog to Digital Converters (ADC0/ADC1)         Fast Analog to Digital Converter (FADC)         Oscillator Pins         Temperature Sensor         Power Supply Current         AC Parameters         Testing Waveforms         Output Rise/Fall Times         Power Sequencing         Power Sequencing         Power, Pad and Reset Timing         Phase Locked Loop (PLL)         BFCLKO Output Clock Timing         Debug Trace Timing         JTAG Interface Timing         Demultiplexed Read Timing         Demultiplexed Read Timing         Demultiplexed Read Timing         BEBU Burst Mode Read Timing         EBU Arbitration Signal Timing         Peripheral Timings         Micro Link Interface (MLI) Timing         Micro Second Channel (MSC) Interface Timing         Synchronous Serial Channel (SSC) Master Mode Timing         Package and Reliability         Package Outline         Flash Memory Parameters |

32-Bit Single-Chip Microcontroller TriCore

## 1 Summary of Features

- High-performance 32-bit super-scalar TriCore V1.3 CPU with 4-stage pipeline

- Superior real-time performance

- Strong bit handling

- Fully integrated DSP capabilities

- Single precision Floating Point Unit (FPU)

- 130 MHz operation at full temperature range

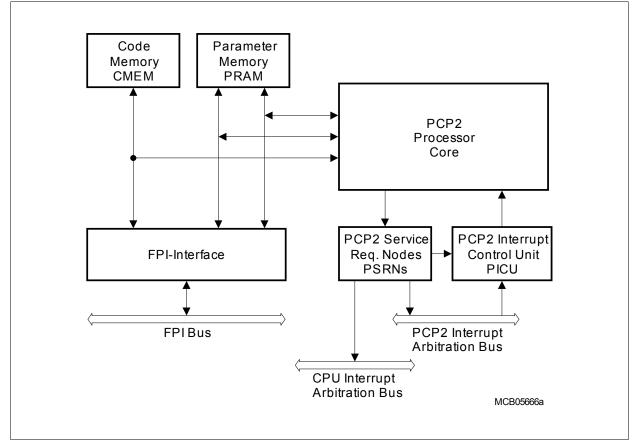

- 32-bit Peripheral Control Processor with single cycle instruction (PCP2)

- 8 KByte Parameter Memory (PRAM)

- 16 KByte Code Memory (CMEM)

- Multiple on-chip memories

- 2 MByte Program Flash Memory (PFLASH) with ECC

- 64 KByte Data Flash Memory (DFLASH) for EEPROM emulation

- 96 KByte Data Memory (LDRAM, SRAM, SBRAM)

- 24 KByte Code Scratchpad Memory (SPRAM)

- 16 KByte Instruction Cache (ICACHE)

- 16 KByte BootROM (BROM)

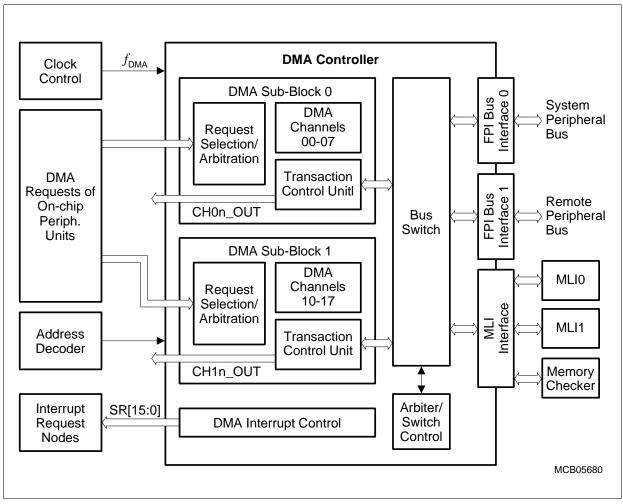

- 16-Channel DMA Controller

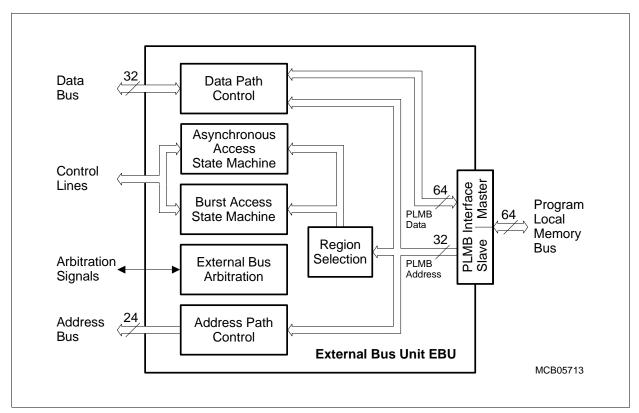

- 32-bit External Bus Interface Unit (EBU) with

- 75 dedicated address/data bus, clock, and control lines

- Synchronous burst Flash access capability

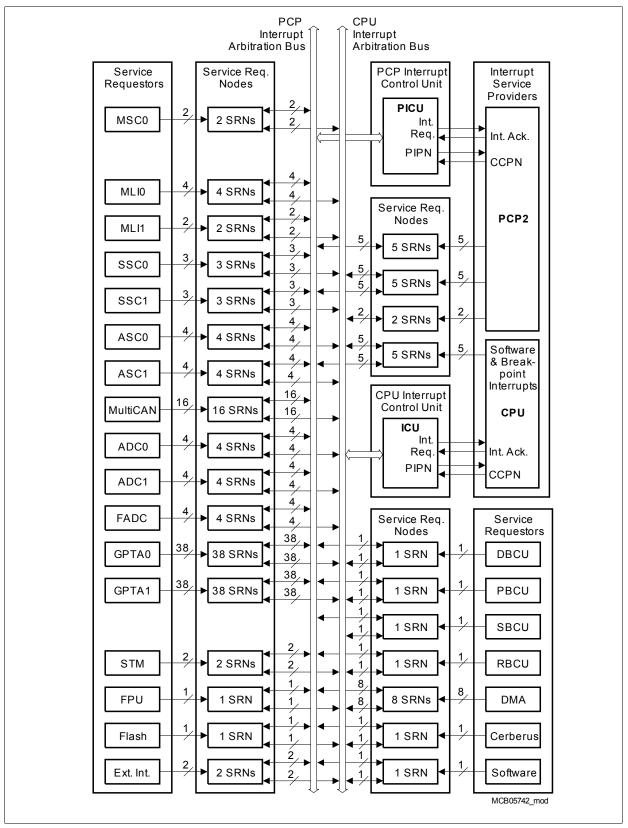

- Sophisticated interrupt system with  $2 \times 255$  hardware priority arbitration levels serviced by CPU or PCP2

- High performing on-chip bus structure

- Two 64-bit Local Memory Buses between EBU, Flash and Data Memory

- 32-bit System Peripheral Bus (SPB) for on-chip peripheral and functional units

- 32-bit Remote Peripheral Bus (RPB) for high-speed on-chip peripheral units

- Two bus bridges (LFI Bridge, DMA Controller)

- Peripheral Control Processor with single cycle instruction (PCP2)

- 8 KByte Parameter Memory (PRAM)

- 16 KByte Code Memory (CMEM)

- Versatile On-chip Peripheral Units

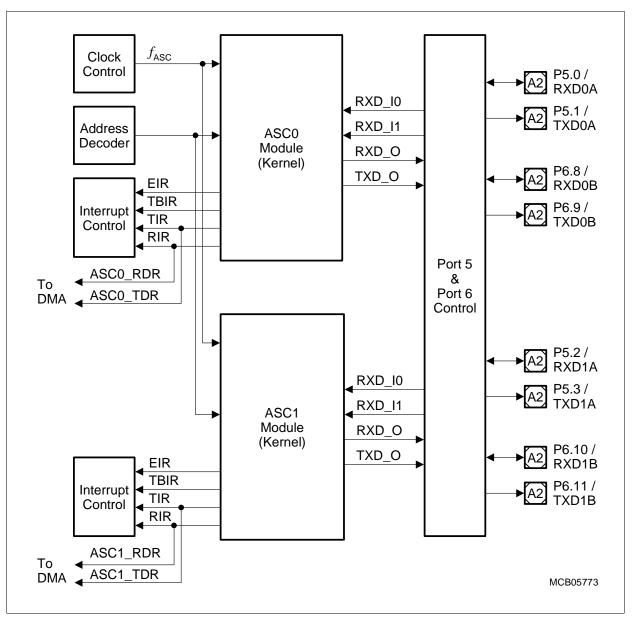

- Two Asynchronous/Synchronous Serial Channels (ASC) with baud rate generator, parity, framing and overrun error detection

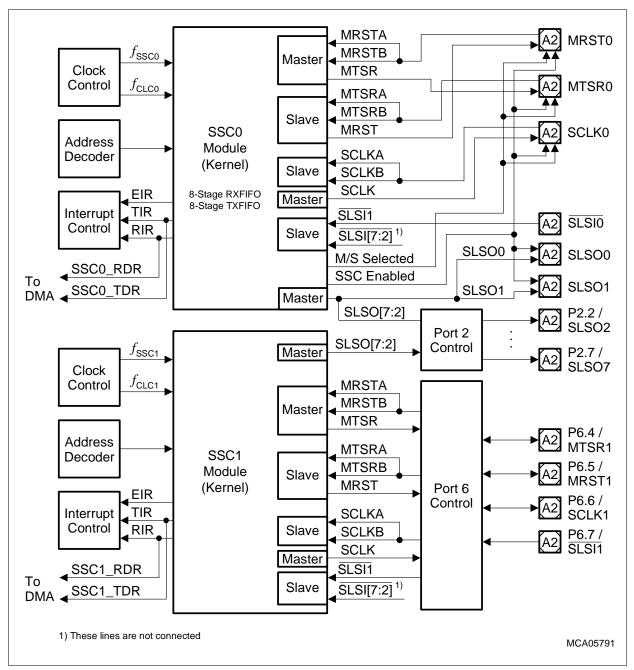

- Two High-Speed Synchronous Serial Channels (SSC) with programmable data length and shift direction

TC1792

#### Summary of Features

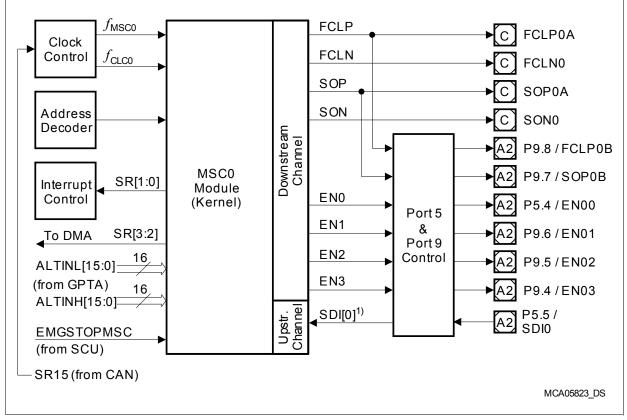

- One serial Micro Second Bus interfaces (MSC) for serial port expansion to external power devices

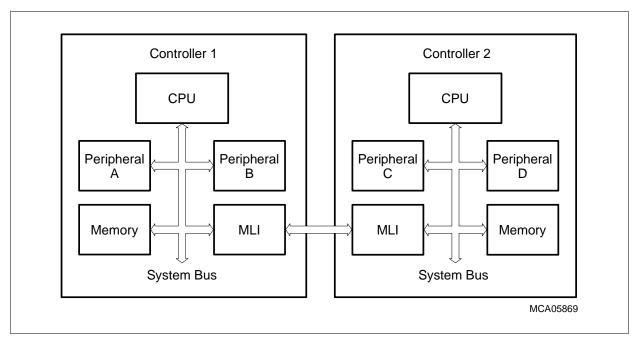

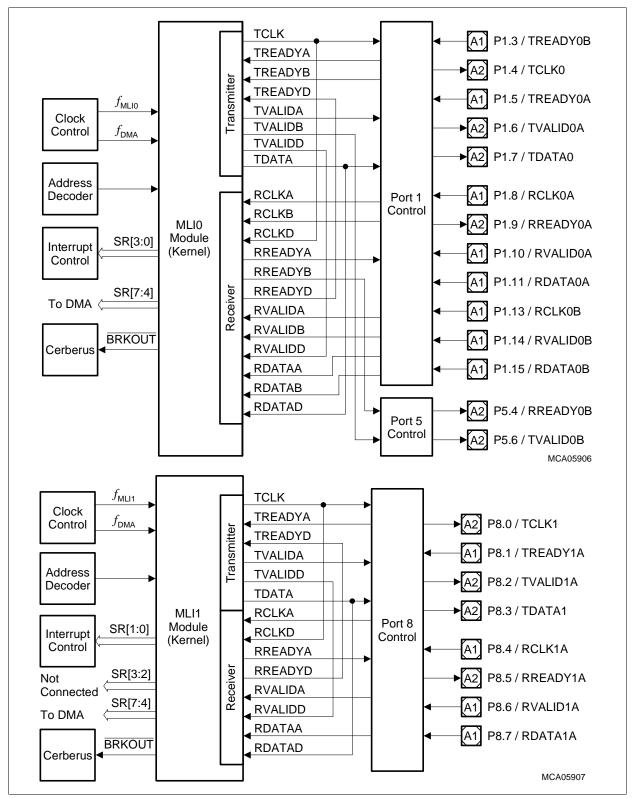

- Two High-Speed Micro Link interfaces (MLI) for serial inter-processor communication

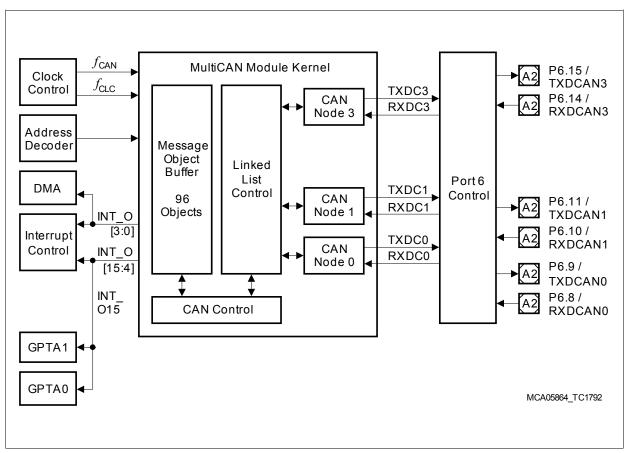

- One MultiCAN Module with three CAN nodes and 96 free assignable message objects for high efficiency data handling via FIFO buffering and gateway data transfer (one CAN node supports TTCAN functionality)

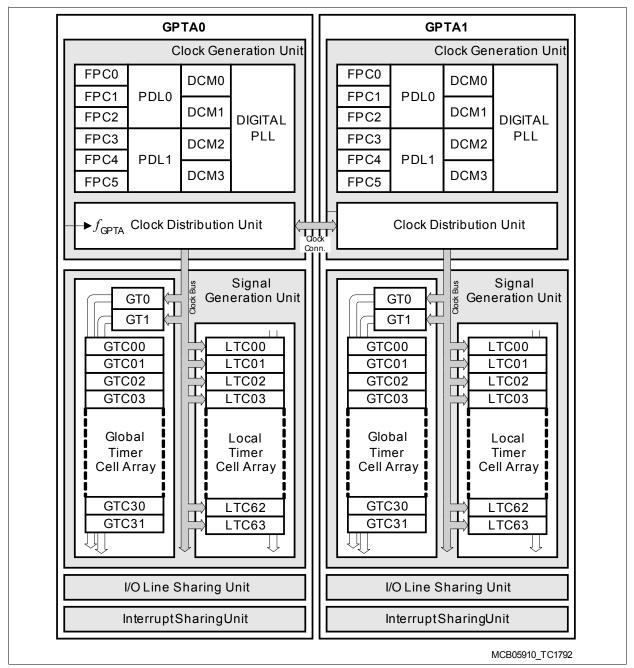

- Two General Purpose Timer Array Modules (GPTA) providing a powerful set of digital signal filtering and timer functionality to realize autonomous and complex Input/Output management

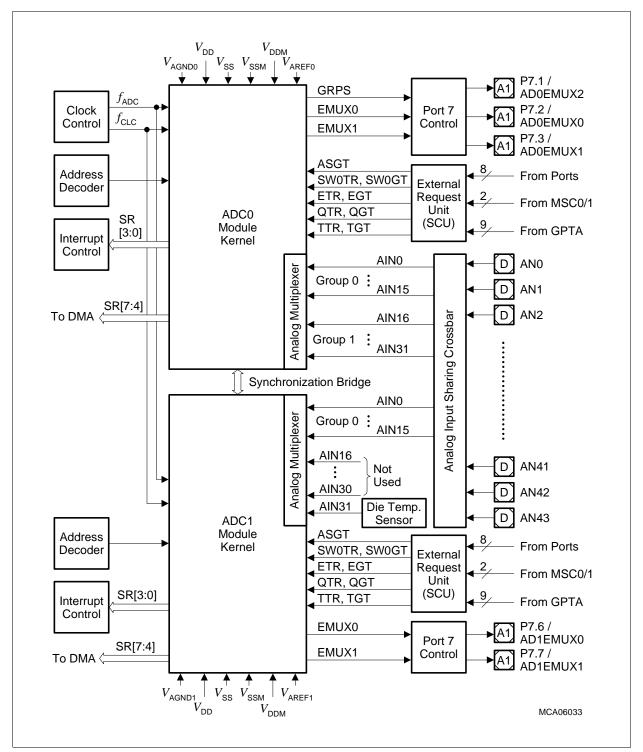

- Two 16-channel Analog-to-Digital Converter units (ADC) with selectable 8-bit, 10bit, or 12-bit resolution

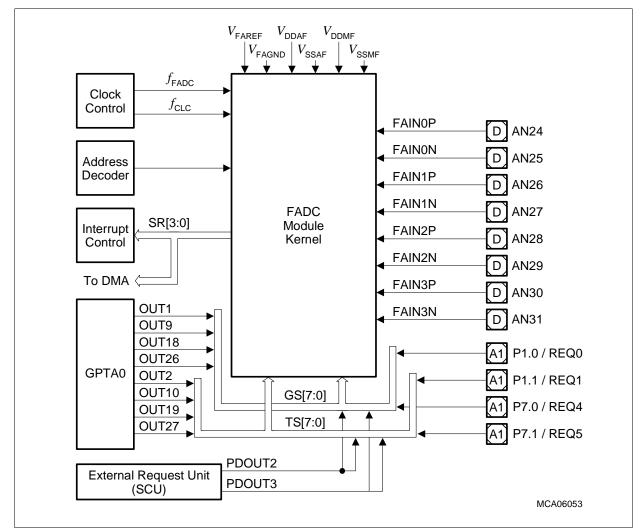

- One 4-channel Fast Analog-to-Digital Converter unit (FADC) with concatenated comb filters for hardware data reduction: supporting 10-bit resolution, min. conversion time of 280ns

- 44 analog input lines for ADC and FADC

- 123 digital general purpose I/O lines, 4 input lines

- Digital I/O ports with 3.3 V capability

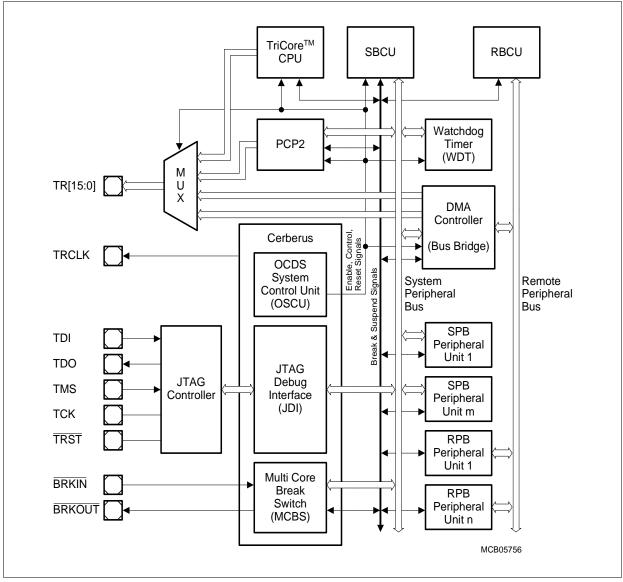

- On-chip debug support for OCDS Level 1 and 2 (CPU, PCP3, DMA)

- Dedicated Emulation Device chip for multi-core debugging, tracing, and calibration via USB V1.1 interface available (TC1796ED)

- Power Management System

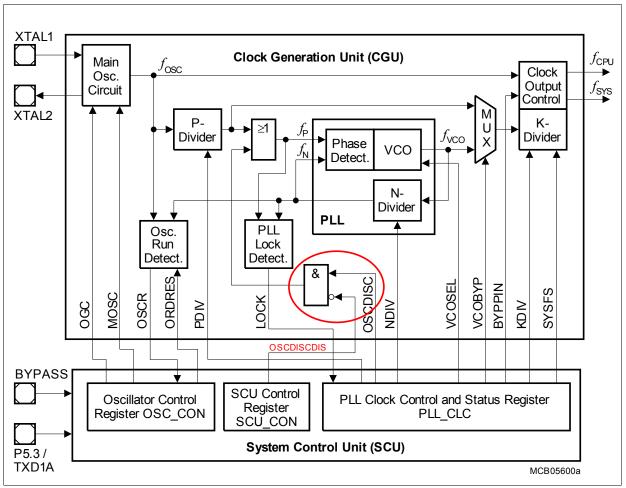

- Clock Generation Unit with PLL

- Core supply voltage of 1.5 V

- I/O voltage of 3.3 V

- Full automotive temperature range: -40° to +125°C

- P-BGA-416-4 package

#### **Summary of Features**

#### **Ordering Information**

The ordering code for Infineon microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- The package and the type of delivery.

For the available ordering codes for the TC1792 please refer to the **"Product Catalog Microcontrollers"**, which summarizes all available microcontroller variants.

This document describes the derivatives of the device. The **Table 1** enumerates these derivatives and summarizes the differences. As this document refers to all of these derivatives, some descriptions may not apply to a specific product.

For simplicity all versions are referred to by the term **TC1792** throughout this document.

#### Table 1TC1792 Derivative Synopsis

| Derivative                        | Ambient Temperature Range                        |

|-----------------------------------|--------------------------------------------------|

| SAK-TC1792-256F130E <sup>1)</sup> | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ |

1) This Data Sheet is valid for devices of design steps AA and AB.

#### **General Device Information**

2 General Device Information

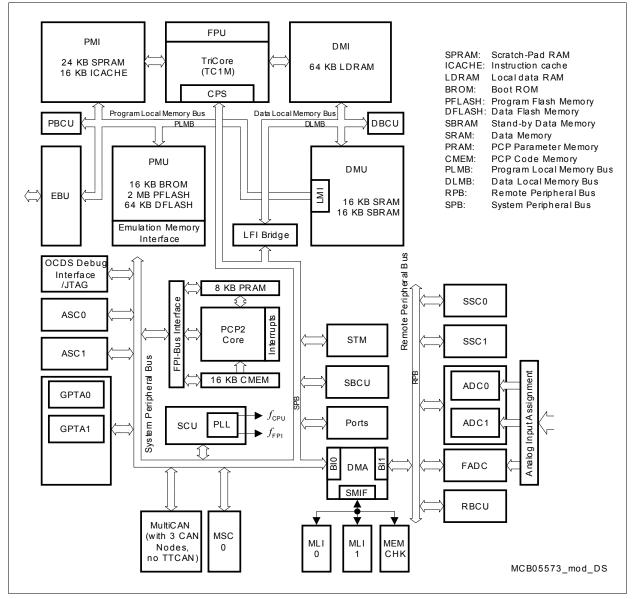

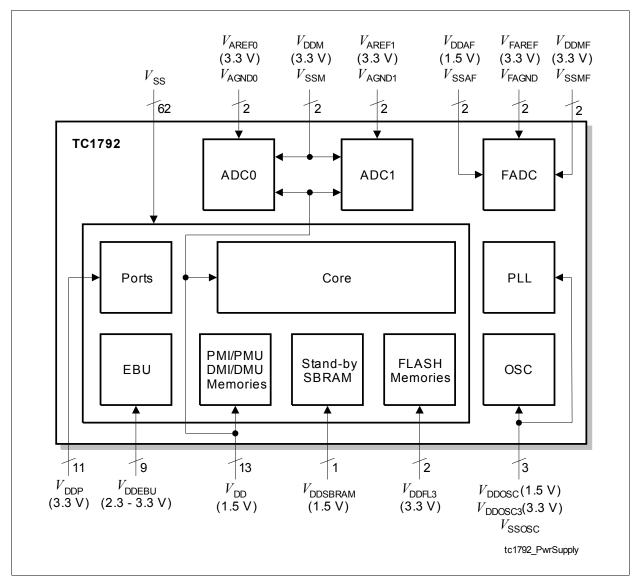

## 2.1 Block Diagram

#### **Advance Information**

#### **General Device Information**

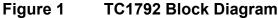

#### 2.2 Logic Symbol

Figure 2 TC1792 Logic Symbol

#### Advance Information

#### **General Device Information**

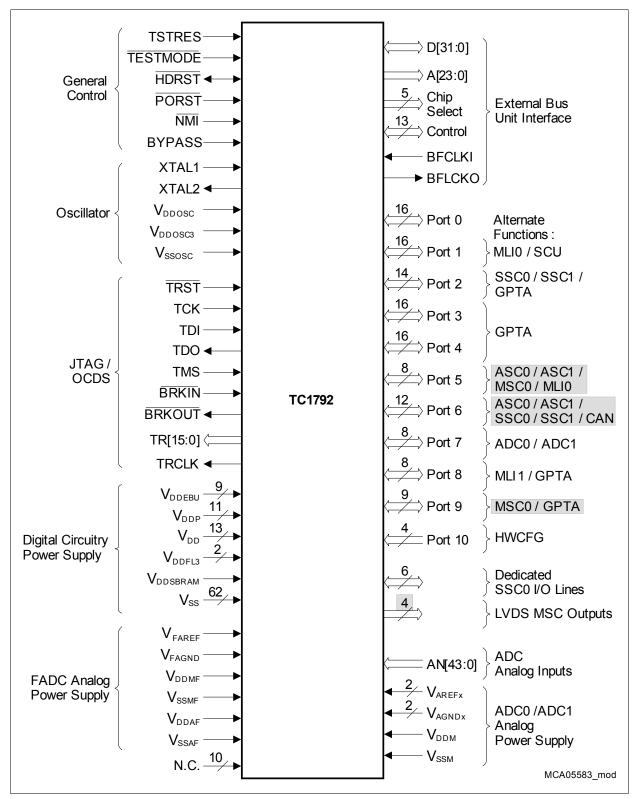

#### 2.3 Pin Configuration

TC1792 Pinning for P-BGA-416-4 Package (Top view)

#### **General Device Information**

#### 2.4 Pad Driver and Input Classes Overview

The TC1792 provides different types and classes of input and output lines. For understanding of the abbreviations in **Table 2** starting at the next page, **Table 10** gives an overview on the pad type and class types.

### **General Device Information**

#### 2.5 Pin Definitions and Functions

| Table 2Pin Definitions and Fu | nctions |

|-------------------------------|---------|

|-------------------------------|---------|

| Symbol                             | Pins | I/O | Pad<br>Class | Power           | Functions                               |  |  |  |

|------------------------------------|------|-----|--------------|-----------------|-----------------------------------------|--|--|--|

|                                    |      |     |              | Supply          |                                         |  |  |  |

| External Bus Interface Lines (EBU) |      |     |              |                 |                                         |  |  |  |

| D[31:0]                            |      | I/O | B1           | $V_{\rm DDEBU}$ | EBU Data Bus Lines                      |  |  |  |

|                                    |      |     |              |                 | The EBU Data Bus lines D[31:0] serve as |  |  |  |

|                                    |      |     |              |                 | external data bus.                      |  |  |  |

| D0                                 | T26  | I/O |              |                 | Data bus line 0                         |  |  |  |

| D1                                 | T24  | I/O |              |                 | Data bus line 1                         |  |  |  |

| D2                                 | U26  | I/O |              |                 | Data bus line 2                         |  |  |  |

| D3                                 | T25  | I/O |              |                 | Data bus line 3                         |  |  |  |

| D4                                 | V26  | I/O |              |                 | Data bus line 4                         |  |  |  |

| D5                                 | U25  | I/O |              |                 | Data bus line 5                         |  |  |  |

| D6                                 | U23  | I/O |              |                 | Data bus line 6                         |  |  |  |

| D7                                 | W26  | I/O |              |                 | Data bus line 7                         |  |  |  |

| D8                                 | V25  | I/O |              |                 | Data bus line 8                         |  |  |  |

| D9                                 | U24  | I/O |              |                 | Data bus line 9                         |  |  |  |

| D10                                | Y26  | I/O |              |                 | Data bus line 10                        |  |  |  |

| D11                                | AA26 | I/O |              |                 | Data bus line 11                        |  |  |  |

| D12                                | W25  | I/O |              |                 | Data bus line 12                        |  |  |  |

| D13                                | V24  | I/O |              |                 | Data bus line 13                        |  |  |  |

| D14                                | Y25  | I/O |              |                 | Data bus line 14                        |  |  |  |

| D15                                | AB26 | I/O |              |                 | Data bus line 15                        |  |  |  |

| D16                                | W24  | I/O |              |                 | Data bus line 16                        |  |  |  |

| D17                                | AA25 | I/O |              |                 | Data bus line 17                        |  |  |  |

| D18                                | Y24  | I/O |              |                 | Data bus line 18                        |  |  |  |

| D19                                | AA23 | I/O |              |                 | Data bus line 19                        |  |  |  |

| D20                                | AB25 | I/O |              |                 | Data bus line 20                        |  |  |  |

| D21                                | AB24 | I/O |              |                 | Data bus line 21                        |  |  |  |

| D22                                | AA24 | I/O |              |                 | Data bus line 22                        |  |  |  |

| D23                                | AC26 | I/O |              |                 | Data bus line 23                        |  |  |  |

| D24                                | AD26 | I/O |              |                 | Data bus line 24                        |  |  |  |

| D25                                | AC25 | I/O |              |                 | Data bus line 25                        |  |  |  |

| D26                                | AE26 | I/O |              |                 | Data bus line 26                        |  |  |  |

| D27                                | AD25 | I/O |              |                 | Data bus line 27                        |  |  |  |

| D28                                | AC24 | I/O |              |                 | Data bus line 28                        |  |  |  |

| D29                                | AE25 | I/O |              |                 | Data bus line 29                        |  |  |  |

| D30                                | AE24 | I/O |              |                 | Data bus line 30                        |  |  |  |

| D31                                | AD24 | I/O |              |                 | Data bus line 31                        |  |  |  |

## **Advance Information**

#### **General Device Information**

| Symbol  | Pins | I/O | Pad<br>Class | Power<br>Supply    | Functions                                                                                                       |

|---------|------|-----|--------------|--------------------|-----------------------------------------------------------------------------------------------------------------|

| A[23:0] |      | 0   | B1           | $V_{\rm DDEBU}$    | EBU Address Bus Lines A[23:0]                                                                                   |

|         |      |     |              |                    | The EBU Address Bus Lines serve as                                                                              |

|         |      |     |              |                    | external address bus.                                                                                           |

| A0      | J24  | 0   |              |                    | Address bus line 0                                                                                              |

| A1      | J25  | 0   |              |                    | Address bus line 1                                                                                              |

| A2      | J26  | 0   |              |                    | Address bus line 2                                                                                              |

| A3      | K25  | 0   |              |                    | Address bus line 3                                                                                              |

| A4      | K26  | 0   |              |                    | Address bus line 4                                                                                              |

| A5      | J23  | 0   |              |                    | Address bus line 5                                                                                              |

| A6      | K24  | 0   |              |                    | Address bus line 6                                                                                              |

| A7      | L25  | 0   |              |                    | Address bus line 7                                                                                              |

| A8      | L26  | 0   |              |                    | Address bus line 8                                                                                              |

| A9      | K23  | 0   |              |                    | Address bus line 9                                                                                              |

| A10     | M26  | 0   |              |                    | Address bus line 10                                                                                             |

| A11     | M25  | 0   |              |                    | Address bus line 11                                                                                             |

| A12     | M24  | 0   |              |                    | Address bus line 12                                                                                             |

| A13     | L24  | 0   |              |                    | Address bus line 13                                                                                             |

| A14     | N26  | 0   |              |                    | Address bus line 14                                                                                             |

| A15     | N23  | 0   |              |                    | Address bus line 15                                                                                             |

| A16     | N24  | 0   |              |                    | Address bus line 16                                                                                             |

| A17     | N25  | 0   |              |                    | Address bus line 17                                                                                             |

| A18     | P26  | 0   |              |                    | Address bus line 18                                                                                             |

| A19     | P24  | 0   |              |                    | Address bus line 19                                                                                             |

| A20     | P25  | 0   |              |                    | Address bus line 20                                                                                             |

| A21     | R24  | 0   |              |                    | Address bus line 21                                                                                             |

| A22     | R26  | 0   |              |                    | Address bus line 22                                                                                             |

| A23     | R25  | 0   |              |                    | Address bus line 23                                                                                             |

|         |      |     | B1           | V <sub>DDEBU</sub> | Chip Select Output Lines                                                                                        |

| CS0     | AE21 | 0   |              | , DDFRO            | Chip select output line 0                                                                                       |

| CS1     | AD21 | 0   |              |                    | Chip select output line 1                                                                                       |

| CS2     | AD20 | 0   |              |                    | Chip select output line 2                                                                                       |

| CS3     | AD19 | 0   |              |                    | Chip select output line 3                                                                                       |

| CSCOMB  | AE19 | 0   | B1           | V <sub>DDEBU</sub> | <b>Combined Chip Select Output</b><br>Used for Global Select / Emulator Memor<br>Region/Emulator Overlay Memory |

## **Advance Information**

#### **General Device Information**

| Table 2                  |                              |                  |              |                    |                                                                                                                |

|--------------------------|------------------------------|------------------|--------------|--------------------|----------------------------------------------------------------------------------------------------------------|

| Symbol                   | Pins                         | I/O              | Pad<br>Class | Power<br>Supply    | Functions                                                                                                      |

| BFCLKO                   | AF25                         | 0                | B2           | V <sub>DDEBU</sub> | Burst Mode Flash Clock Output (non-<br>differential)                                                           |

| BFCLKI                   | AF24                         | I                | B1           | -                  | Burst Mode Flash Clock Input<br>(feedback clock)                                                               |

| RD                       | AF20                         | 0                | B1           |                    | Read Control Line                                                                                              |

| RD/WR                    | AF21                         | 0                | B1           | -                  | Write Control Line                                                                                             |

| ADV                      | AF22                         | 0                | B1           | -                  | Address Valid Output                                                                                           |

| BC0<br>BC1<br>BC2<br>BC3 | AE17<br>AD17<br>AF18<br>AE18 | 0<br>0<br>0<br>0 | B1           |                    | Byte Control Lines<br>Byte control line 0<br>Byte control line 1<br>Byte control line 2<br>Byte control line 3 |

| MR/W                     | AF19                         | 0                | B1           |                    | Motorola-style Read/Write Control<br>Signal                                                                    |

| WAIT                     | AE20                         | I                | B1           | -                  | Wait Input for inserting Wait-States                                                                           |

| BAA                      | AF23                         | 0                | B1           |                    | Burst Address Advance Output                                                                                   |

| HOLD                     | AF17                         | I                | B1           |                    | Hold Request Input                                                                                             |

| HLDA                     | AD18                         | 0                | B1           |                    | Hold Acknowledge Output                                                                                        |

| BREQ                     | AD22                         | 0                | B1           |                    | Bus Request Output                                                                                             |

## Table 2Pin Definitions and Functions (cont'd)

## Advance Information

#### **General Device Information**

## **Advance Information**

## **General Device Information**

| Table 2     Pin Definitions and Functions (cont'd) |      |     |              |                  |                  |                                        |  |

|----------------------------------------------------|------|-----|--------------|------------------|------------------|----------------------------------------|--|

| Symbol                                             | Pins | I/O | Pad<br>Class | Power<br>Supply  | Functions        |                                        |  |

| P1                                                 |      | I/O | A1/A2        | V <sub>DDP</sub> | Port 1           |                                        |  |

|                                                    |      |     |              |                  | Port 1 is a 16-  | -bit bidirectional general             |  |

|                                                    |      |     |              |                  | purpose I/O p    | ort which can be alternatively         |  |

|                                                    |      |     |              |                  |                  | /ILI0 interface or as external         |  |

|                                                    |      |     |              |                  | trigger input li |                                        |  |

| P1.0                                               | P3   | I   | A1           |                  | REQ0             | External trigger input 0               |  |

| P1.1                                               | P2   | I   | A1           |                  | REQ1             | External trigger input 1               |  |

| P1.2                                               | P1   | I   | A1           |                  | REQ2             | External trigger input 2               |  |

| P1.3                                               | N1   | I   | A1           |                  | REQ3             | External trigger input 3               |  |

|                                                    |      | I   |              |                  | TREADY0B         | MLI0 transmit channel<br>ready input B |  |

| P1.4                                               | N4   | 0   | A2           |                  | TCLK0            | MLI0 transmit channel clock            |  |

|                                                    |      |     |              |                  |                  | output                                 |  |

| P1.5                                               | M4   | I   | A1           |                  | TREADY0A         | MLI0 transmit channel                  |  |

|                                                    |      |     |              |                  |                  | ready input A                          |  |

| P1.6                                               | N3   | 0   | A2           |                  | TVALID0A         | MLI0 transmit channel valid            |  |

|                                                    |      |     |              |                  |                  | output A                               |  |

| P1.7                                               | N2   | 0   | A2           |                  | TDATA0           | MLI0 transmit channel data             |  |

|                                                    |      |     |              |                  |                  | output                                 |  |

| P1.8                                               | M3   | I   | A1           |                  | RCLK0A           | MLI0 receive channel clock             |  |

|                                                    |      |     |              |                  |                  | input A                                |  |

| P1.9                                               | M2   | 0   | A2           |                  | RREADY0A         | MLI0 receive channel ready             |  |

|                                                    |      |     |              |                  |                  | output A                               |  |

| P1.10                                              | M1   | I   | A1           |                  | RVALID0A         | MLI0 receive channel valid             |  |

|                                                    |      |     |              |                  |                  | input A                                |  |

| P1.11                                              | L4   | I   | A1           |                  | RDATA0A          | MLI0 receive channel data              |  |

|                                                    |      |     |              |                  |                  | input A                                |  |

| P1.12                                              | P4   | 0   | A2           |                  | SYSCLK           | System clock output                    |  |

| P1.13                                              | L3   | I   | A1           |                  | RCLK0B           | MLI0 receive channel clock             |  |

|                                                    |      |     |              |                  |                  | input B                                |  |

| P1.14                                              | L2   | I   | A1           |                  | RVALID0B         | MLI0 receive channel valid             |  |

|                                                    |      |     |              |                  |                  | input B                                |  |

| P1.15                                              | L1   | I   | A1           |                  | RDATA0B          | MLI0 receive channel data              |  |

|                                                    |      |     |              |                  |                  | input B                                |  |

## Table 2Pin Definitions and Functions (cont'd)

## Advance Information

### **General Device Information**

| Table 2                                                                                                                                     | Pin Definitions and Functions (cont'd)                                                                     |                                                                    |                                                                                        |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                                                                                                                                      | Pins                                                                                                       | I/O                                                                | Pad<br>Class                                                                           | Power<br>Supply  | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| P2                                                                                                                                          |                                                                                                            | I/O                                                                | A1/A2                                                                                  | V <sub>DDP</sub> | <b>Port 2</b><br>Port 2 is a 14-bit bidirectional general<br>purpose I/O port which can be used<br>alternatively for the six upper SSC slave<br>select outputs or for GPTA I/O lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| P2.2<br>P2.3<br>P2.4<br>P2.5<br>P2.6<br>P2.7<br>P2.8<br>P2.9<br>P2.10<br>P2.11<br>P2.12<br>P2.12<br>P2.13<br>P2.14<br>P2.15                 | D3<br>D2<br>D1<br>C1<br>B1<br>B2<br>C2<br>A2<br>B3<br>C3<br>C3<br>C4<br>A3<br>B4<br>A4                     | 0<br>0<br>0<br>0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0<br>1/0  | A2<br>A2<br>A2<br>A2<br>A2<br>A1<br>A1<br>A1<br>A1<br>A1<br>A1<br>A1<br>A1<br>A1<br>A1 |                  | SLSO2Slave select output line 2SLSO3Slave select output line 3SLSO4Slave select output line 4SLSO5Slave select output line 5SLSO6Slave select output line 6SLSO7Slave select output line 7IN0 / OUT0 line of GPTAIN1 / OUT1 line of GPTAIN2 / OUT2 line of GPTAIN3 / OUT3 line of GPTAIN4 / OUT4 line of GPTAIN5 / OUT5 line of GPTAIN5 / OUT5 line of GPTAIN6 / OUT6 line of GPTAIN7 / OUT7 line of GPTAIN7 / OUT7 line of GPTA                                                                                                                                                                                                       |  |  |  |

| P3.0<br>P3.1<br>P3.2<br>P3.3<br>P3.4<br>P3.5<br>P3.6<br>P3.7<br>P3.8<br>P3.9<br>P3.10<br>P3.10<br>P3.11<br>P3.12<br>P3.13<br>P3.14<br>P3.15 | B12<br>A12<br>C13<br>B11<br>C12<br>A11<br>B10<br>C9<br>D10<br>C11<br>C10<br>D13<br>D11<br>D12<br>A10<br>B9 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | A1                                                                                     | V <sub>DDP</sub> | Port 3<br>Port 3 is a 16-bit bidirectional general<br>purpose I/O port which can be alternatively<br>used for GPTA I/O lines.<br>IN8 / OUT8 line of GPTA<br>IN9 / OUT9 line of GPTA<br>IN10 / OUT10 line of GPTA<br>IN11 / OUT11 line of GPTA<br>IN12 / OUT12 line of GPTA<br>IN12 / OUT12 line of GPTA<br>IN13 / OUT13 line of GPTA<br>IN14 / OUT14 line of GPTA<br>IN15 / OUT15 line of GPTA<br>IN16 / OUT16 line of GPTA<br>IN17 / OUT17 line of GPTA<br>IN18 / OUT18 line of GPTA<br>IN19 / OUT19 line of GPTA<br>IN20 / OUT20 line of GPTA<br>IN21 / OUT21 line of GPTA<br>IN22 / OUT22 line of GPTA<br>IN23 / OUT23 line of GPTA |  |  |  |

#### **Advance Information**

#### **General Device Information**

| Table 2 | Pin Definitions and Functions (cont'd) |     |                  |                  |                                                                                                                                      |  |  |  |

|---------|----------------------------------------|-----|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol  | Pins                                   | I/O | Pad<br>Class     | Power<br>Supply  | Functions                                                                                                                            |  |  |  |

| P4      |                                        | I/O | A1/A2            | V <sub>DDP</sub> | <b>Port 4</b><br>Port 4 is a 16-bit bidirectional general<br>purpose I/O port which can be alternatively<br>used for GPTA I/O lines. |  |  |  |

| P4.0    | AD10                                   | I/O | A2 <sup>1)</sup> |                  | IN24 / OUT24 line of GPTA                                                                                                            |  |  |  |

| P4.1    | AE10                                   | I/O | A2 <sup>1)</sup> |                  | IN25 / OUT25 line of GPTA                                                                                                            |  |  |  |

| P4.2    | AD11                                   | I/O | A2 <sup>1)</sup> |                  | IN26 / OUT26 line of GPTA                                                                                                            |  |  |  |

| P4.3    | AE11                                   | I/O | A2 <sup>1)</sup> |                  | IN27 / OUT27 line of GPTA                                                                                                            |  |  |  |

| P4.4    | AC12                                   | I/O | A2 <sup>1)</sup> |                  | IN28 / OUT28 line of GPTA                                                                                                            |  |  |  |

| P4.5    | AD12                                   | I/O | A2 <sup>1)</sup> |                  | IN29 / OUT29 line of GPTA                                                                                                            |  |  |  |

| P4.6    | AF10                                   | I/O | A2 <sup>1)</sup> |                  | IN30 / OUT30 line of GPTA                                                                                                            |  |  |  |

| P4.7    | AE12                                   | I/O | A2 <sup>1)</sup> |                  | IN31 / OUT31 line of GPTA                                                                                                            |  |  |  |

| P4.8    | AC13                                   | I/O | A1               |                  | IN32 / OUT32 line of GPTA                                                                                                            |  |  |  |

| P4.9    | AF11                                   | I/O | A1               |                  | IN33 / OUT33 line of GPTA                                                                                                            |  |  |  |

| P4.10   | AF12                                   | I/O | A1               |                  | IN34 / OUT34 line of GPTA                                                                                                            |  |  |  |

| P4.11   | AD13                                   | I/O | A1               |                  | IN35 / OUT35 line of GPTA                                                                                                            |  |  |  |

| P4.12   | AC14                                   | I/O | A1               |                  | IN36 / OUT36 line of GPTA                                                                                                            |  |  |  |

| P4.13   | AE13                                   | I/O | A1               |                  | IN37 / OUT37 line of GPTA                                                                                                            |  |  |  |

| P4.14   | AF13                                   | I/O | A1               |                  | IN38 / OUT38 line of GPTA                                                                                                            |  |  |  |

| P4.15   | AD14                                   | I/O | A1               |                  | IN39 / OUT39 line of GPTA                                                                                                            |  |  |  |

<sup>1)</sup> In order to minimize noise coupling to the on-chip A/D converters, it is recommended to use these pins as less as possible in strong driver mode.

## **General Device Information**

| Symbol       | Pins       | I/O      | Pad<br>Class | Power<br>Supply  | Functions        |                                                                                                                                                                                     |

|--------------|------------|----------|--------------|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P5           |            | I/O      | A2           | V <sub>DDP</sub> | purpose I/O      | 8-bit bidirectional general<br>port which can be alternatively<br>C0/1 or MSC0/1 lines.                                                                                             |

| P5.0<br>P5.1 | B13<br>A13 | I/O<br>O |              |                  | RXD0A<br>TXD0A   | ASC0 receiver input/output A<br>ASC0 transmitter output A                                                                                                                           |

| P5.2<br>P5.3 | A14<br>B14 | I/O<br>O |              |                  | RXD1A<br>TXD1A   | ASC1 receiver input/output A<br>ASC1 transmitter output A<br>P5.3 is latched with the rising<br>edge of PORST if BYPASS = 1<br>and stored in inverted state as<br>bit OSC CON.MOSC. |

| P5.4         | C15        | 0<br>0   |              |                  | EN00<br>RREADY0B | MSC0 device select output 0<br>3 MLI0 receive channel ready<br>output B                                                                                                             |

| P5.5<br>P5.6 | C14<br>B15 | I<br>O   |              |                  | SDI0<br>TVALID0B | MSC0 serial data input<br>MLI0 transmit channel valid<br>output B                                                                                                                   |

| P5.7         | A15        | 1        |              |                  |                  | -                                                                                                                                                                                   |

#### Table 2Pin Definitions and Functions (cont'd)

## **Advance Information**

## **General Device Information**

| Symbol | Pins | I/O | Pad<br>Class | Power<br>Supply  | Functions     |                                  |

|--------|------|-----|--------------|------------------|---------------|----------------------------------|

| P6     |      | I/O | A2           | V <sub>DDP</sub> | Port 6        |                                  |

|        |      |     |              |                  | Port 6 is a 1 | 2-bit bidirectional general      |

|        |      |     |              |                  | purpose I/O   | port which can be alternatively  |

|        |      |     |              |                  | used for SS   | C1, ASC0/1, and CAN I/O lines.   |

| P6.4   | F3   | 0   |              |                  | MTSR1         | SSC1 master transmit output /    |

|        |      | I   |              |                  |               | SSC1 slave receive input         |

| P6.5   | G4   | I   |              |                  | MRST1         | SSC1 master receive input /      |

|        |      | 0   |              |                  |               | SSC1 slave transmit output       |

| P6.6   | E3   | I/O |              |                  | SCLK1         | SSC1 clock input/output          |

| P6.7   | G3   | I   |              |                  | SLSI1         | SSC1 slave select input          |

| P6.8   | F4   | I   |              |                  | RXDCAN0       | CAN node 0 receiver input        |

|        |      | I/O |              |                  | RXD0B         | ASC0 receiver input/output B     |

| P6.9   | E4   | 0   |              |                  | TXDCAN0       | CAN node 0 transmitter<br>output |

|        |      | 0   |              |                  | TXD0B         | ASC0 transmitter output B        |

| P6.10  | F2   | I   |              |                  | RXDCAN1       | CAN node 1 receiver input        |

|        |      | I/O |              |                  | RXD1B         | ASC1 receiver in/out B           |

| P6.11  | E2   | 0   |              |                  | TXDCAN1       | CAN node 1 transmitter           |

|        |      |     |              |                  |               | output                           |

|        |      | 0   |              |                  | TXD1B         | ASC1 transmitter output B        |

| P6.12  | E1   | I   |              |                  | -             |                                  |

| P6.13  | G2   | 0   |              |                  | -             |                                  |

| P6.14  | F1   | I   |              |                  | RXDCAN3       | CAN node 3 receiver input        |

| P6.15  | G1   | 0   |              |                  | TXDCAN3       | CAN node 3 transmitter output    |

## **Advance Information**

## **General Device Information**

| Symbol | Pins | I/O | Pad<br>Class | Power<br>Supply  | Functions                      |                                                                                                                             |

|--------|------|-----|--------------|------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| P7     |      | I/O | A1           | V <sub>DDP</sub> | purpose I/O p<br>used as exter | -bit bidirectional general<br>ort which can be alternatively<br>nal trigger input lines and for<br>nal multiplexer control. |

| P7.0   | R3   | I   |              |                  | REQ4                           | External trigger input 4                                                                                                    |

| P7.1   | R2   | I   |              |                  | REQ5                           | External trigger input 5                                                                                                    |

|        |      | 0   |              |                  | AD0EMUX2                       | ADC0 external multiplexer control output 2                                                                                  |

| P7.2   | U4   | 0   |              |                  | AD0EMUX0                       | ADC0 external multiplexer control output 0                                                                                  |

| P7.3   | U3   | 0   |              |                  | AD0EMUX1                       | ADC0 external multiplexer control output 1                                                                                  |

| P7.4   | Т3   | I   |              |                  | REQ6                           | External trigger input 6                                                                                                    |

| P7.5   | T2   | I   |              |                  | REQ7                           | External trigger input 7                                                                                                    |

| P7.6   | T1   | 0   |              |                  | AD1EMUX0                       | ADC1 external multiplexer control output 0                                                                                  |

| P7.7   | U2   | 0   |              |                  | AD1EMUX1                       | ADC1 external multiplexer control output 1                                                                                  |

#### Table 2Pin Definitions and Functions (cont'd)

## **Advance Information**

## **General Device Information**

|      | T                                                                                 |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pins | I/O                                                                               | Pad<br>Class                                                                                                                                                                                              | Power<br>Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Functions                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | I/O                                                                               | A1/A2                                                                                                                                                                                                     | V <sub>DDP</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Port 8                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                                                                                   |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Port 8 is an 8-I                                                                                                               | bit bidirectional general                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |                                                                                   |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                | ort which can be alternatively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

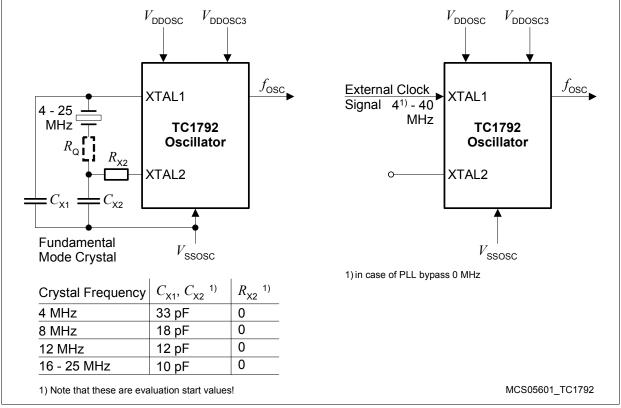

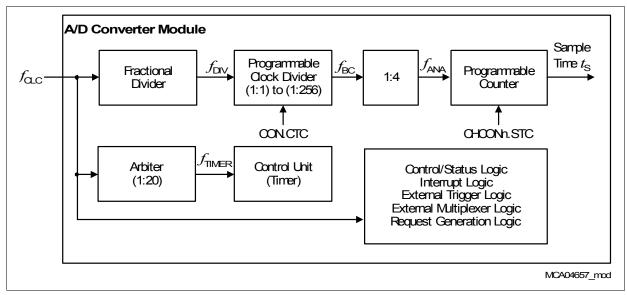

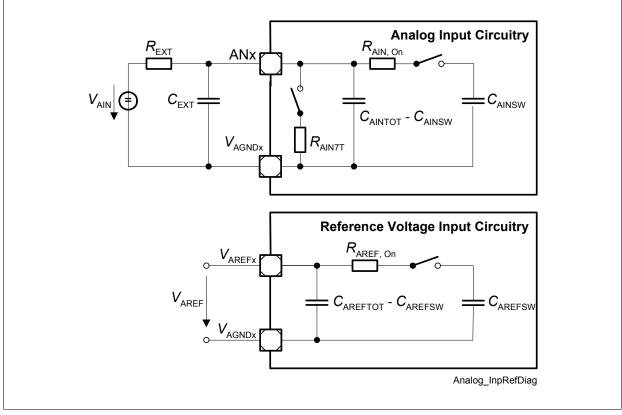

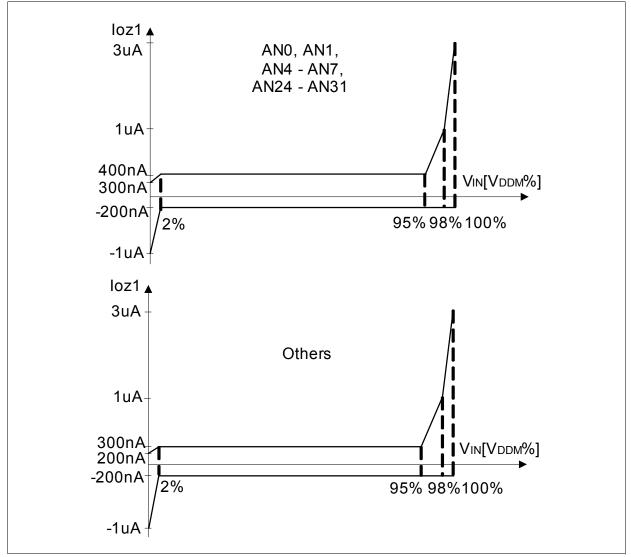

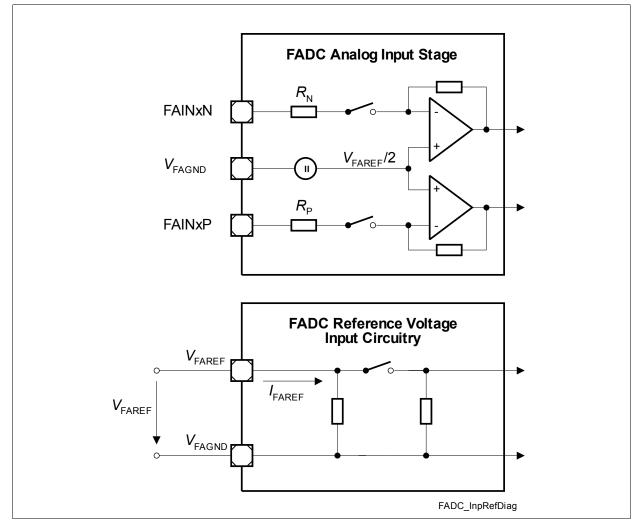

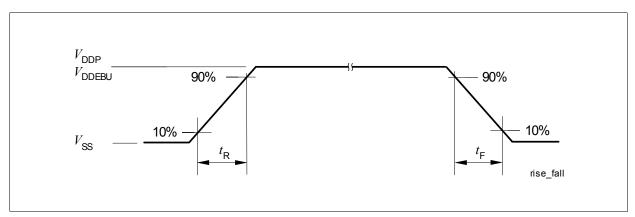

|      |                                                                                   |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                | LI1 interface or as GPTA I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |